界面構造制御による超高速半導体デバイス材料の高信頼性化

今日、人々の生活に不可欠となっている電子機器は、ユビキタス社会の実現に向けて更なる進化を続けており、PC,携帯電話,AV機器などは特に多機能化・高性能化が急速に押し進められている。 これらの電子機器には情報を処理するための大規模集積回路(LSI)が存在する。 LSIはコンピューターの中枢といえるもので、処理能力を左右する重要な部位であるとともに、電子機器の性能に大きく寄与するものである。

現在、電子機器の更なる高性能化のため、次世代の超大規模集積回路(ULSI)の開発が進められており、高集積化と情報処理の高速化を両立すべく多くの研究が取り組まれている。

LSI中の微細銅配線

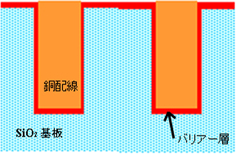

高集積化・高速化を実現するための方法の1つとして、金属配線の微細化が挙げられる。 LSI中の金属配線は図1に示すように、SiO2基板に掘った配線形状の溝(トレンチ)に配線膜を形成し、上部の余分な配線膜を除去することににより形成される(ダマシン法)。 金属配線の微細化とは、この銅配線の配線幅と間隔(ピッチ幅)を小さくすることを意味する。

現在、最先端のデバイスに用いられているLSIの配線幅は90nm(十万分の9ミリ)であり、次世代のULSIを実現するにはさらに配線幅・ピッチを小さくすることが必要になる。

しかしながら、現行の90nm世代のプロセスではこれ以上の微細化は難しく、いくつかの課題を克服する必要がある。

最も重要な課題はバリア層の薄肉化である。 図1に示したように配線とSiO2基板の間にはバリア層が存在する。これはCu(銅)のSi(シリコン)中への拡散を防ぐために不可欠なものであり、バリア性が不十分だとリーク電流の増加などデバイス性能の低下(すなわち故障)を招いてしまう。

図1

現行のプロセスではスパッタリングによってTa,TaNバリア層を成膜しているが、微細化によって側面への成膜が困難になるなどの理由から、バリア層の薄肉化は十数nm程度までしか進んでいない。 技術ロードマップでは2010年で配線幅45nmが目標とされているため、現行のプロセスでは配線幅に対してバリア層の厚さが大きくなり、配線ピッチや実行抵抗の点で大きな問題となってしまう。

本研究室では、薄型・高信頼性のバリア層を形成させる”バリア層自己形成プロセス”の研究に取り組んできた。

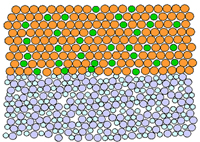

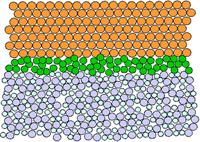

「自己形成プロセス」とは、拡散バリア層となる金属元素を予め銅薄膜中に添加し、熱処理によってSiO2/Cu界面に移動させ、拡散バリア層を自己形成させる手法のことである。 この手法を用いると、バリア層を均一化・薄肉化できるだけでなく、バリア層形成過程の一切を省略することができため、工業的にコスト削減にもつながる。 ただし、これまでにこの自己形成プロセスを実現した報告は存在しない。

熱処理

合金薄膜

バリア層形成

SiO2

Cu合金

バリア層

本研究室では、Cuに添加する合金元素に注目し、材料科学的知見から最適な添加元素を見出すことにより、これまでに自己形成バリアの形成に成功している。

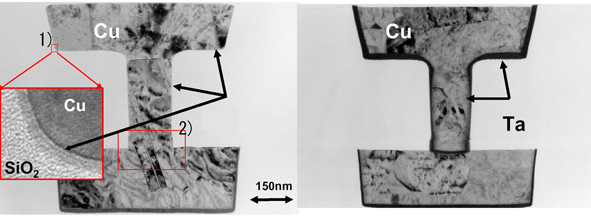

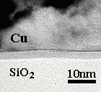

図2に自己形成されたバリア層の例を示す。 CuとSiO2基板の間に厚さ数nmのバリア層が形成されている。 これまでの研究によって、この厚さ数nmのバリア層の特性は良好で、熱的負荷によってもそのバリア性が維持されることが明らかになっている。

図2

図3は実際のダマシン法によって製作された配線の断面図である。 従来のTaを用いたバリア層(右)では、バリア層が厚く、厚さが場所により不均一なのがわかる。 これが従来プロセスの微細化の限界を意味しているといえる。 一方、本研究室で実現した自己形成プロセス(左)では極薄のバリア層が形成されているのがわかる。(拡大図でなければ見えない)

また、左図の赤枠(右)で示した部分には、従来プロセス(右図)にみられるビア底部のバリア層が存在しないことがわかる。このビア底部は電気の通り道となるので、バリア層は存在しないことが望ましい。この点においても、従来プロセスに対してこの自己形成プロセスが優れていることがわかる。

以上述べたように、本研究室の取り組みによって更なる微細化の実現が可能となり、プロセスの簡略化や断線寿命の大幅な向上などが達成されることになる。

本研究室ではこの他にも、自己形成バリアによるLSIの高速化・高集積化に関する研究を行っている。

図3

このページは2005年6月28日(NHK)、2005年6月29日(日経産業新聞、読売新聞、河北新報)、日経マイクロデバイス7月号掲載された内容について、本研究室が独自により詳しく・わかりやすく書いたものです

本研究室では、超高速半導体デバイス(ULSI)の信頼性を向上させるため、界面構造の制御に関する研究を行っております。 ULSIでは数十nmオーダーの技術が使われているため、拡散などによって界面(例えば配線と基板)の構造が崩れることは直ちにデバイスの故障につながります。 すなわち、信頼性のある界面を実現することがデバイスの信頼性向上につながるわけです。

本研究室は、この「界面構造の制御」という重要な課題に関して研究を行い、デバイスの高性能化・高信頼性化に取りくんでいます。